# Effect of self-heating on electrical characteristics of AIGaN/ GaN HEMT on Si (111) substrate

Adarsh Nigam,<sup>1</sup> Thirumaleshwara N. Bhat,<sup>2</sup> Saravanan Rajamani,<sup>1</sup> Surani Bin Dolmanan,<sup>2</sup> Sudhiranjan Tripathy,<sup>2</sup> and Mahesh Kumar<sup>1</sup>, a <sup>1</sup>Department of Electrical Engineering, Indian Institute of Technology Jodhpur, Jodhpur 342011, India

<sup>2</sup>Institute of Materials Research and Engineering, A\*STAR (Agency for Science, Technology and Research), 3 Research Link, Singapore 117602

(Received 19 June 2017; accepted 15 August 2017; published online 25 August 2017)

In order to study the effect of self-heating of AlGaN/ GaN high electron mobility transistors (HEMTs) characteristics fabricated on Si(111) substrate, simulations of 2DEG temperature on different drain voltages have been carried out by Sentaurus TCAD simulator tool. Prior to the electrical direct-current (DC) characteristics studies, structural properties of the HEMT structures were examined by scanning transmission electron microscopy. The comparative analysis of simulation and experimental data provided sheet carrier concentration, mobility, surface traps, electron density at 2DEG by considering factors such as high field saturation, tunneling and recombination models. Mobility, surface trap concentration and contact resistance were obtained by TCAD simulation and found out to be  $\sim 1270 \text{cm}^2/\text{Vs}$ ,  $\sim 2 \times 10^{13} \text{ cm}^{-2}$  and  $\sim 0.2 \Omega$ .mm, respectively, which are in agreement with the experimental results. Consequently, simulated current-voltage characteristics of HEMTs are in good agreement with experimental results. The present simulator tool can be used to design new device structures for III-nitride technology. © 2017 Author(s). All article content, except where otherwise noted, is licensed under a Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/). [http://dx.doi.org/10.1063/1.4990868]

## I. INTRODUCTION

The GaN based materials system has proved its capability for high power, high frequency and high temperature devices due to its wide band gap, high saturation velocity and high breakdown voltage. 1-4 Epitaxial AlGaN/GaN heterostructure forms two-dimensional electron gas (2DEG) at the interface due to the unique polarization properties of III-Nitride materials.<sup>5,6</sup> The spontaneous polarization and piezoelectric polarizations play an important role in the formation of 2DEG at the AlGaN/GaN interfaces. Despite the lack of availability of large area bulk GaN wafers for the growth of epitaxial GaN based layers, heteroepitaxy with the Sapphire and Silicon substrates are most commonly used. A considerable amount of research has been carried out on GaN/sapphire<sup>7,8</sup> but the problem of poor thermal conductivity of sapphire limits itself for high power and high temperature applications. Despite large lattice mismatch, Si has become the most interesting candidate as a substrate for AlGaN/GaN high electron mobility transistor (HEMT) due to the availability of large size wafers (12-inch) and integration possibility with current silicon micro-electronics technology. In addition, Si provides an acceptable thermal conductivity of 1.3W/ (cm. K) for nitride devices. <sup>10,11</sup> Different orientations of Si were studied for GaN HEMT by various research groups to investigate efficient power device platforms. Boulay et al. 12 demonstrated GaN HEMTs on (001) oriented Si substrate for microwave power application. The Si (001) possess four-fold symmetry that is suitable for growth of cubic phase but the Si (111) provides a hexagonal symmetry surface which is more suitable for epitaxial growth of wurtzite phase. 13

<sup>&</sup>lt;sup>a</sup>Correspondence and requests for materials should be addressed to Mahesh Kumar (email: mkumar@iitj.ac.in)

In the present report, discussion on AlGaN/GaN HEMT structures and devices grown on Si wafers will be carried out. A stack of stress relieving AlN and AlGaN buffer layers were grown prior to deposition of GaN over Si, the complete details of typical layer structures are reported in our previous report.<sup>14</sup> Dabiran et al.<sup>15</sup> achieved high electron mobility and very low sheet resistance by variation of Al mole fraction in AlGaN barrier layer. On the top of AlGaN, a cap layer is used to reduce gate leakage and to increase Schottky barrier height. Routine device fabrication to optimize the layer structures and device design is a very time-consuming process, and in this context, a technology computer aided design (TCAD) tool is very helpful which simulates the device according to device physics and analyze characteristics of the device under the desired environment. The Sentaurus TCAD simulator tool is used for the device simulation that solves Poisson equation and continuity equation for both electron and holes for I-V characterization of the device. Physical models that defined in sentaurus TCAD are used for analyzing bandgap, carrier mobility, gate tunneling, charge transport, piezoelectric polarization for device characteristics. Since these device models directly related to the physics of the device thus selection of the proper model for the device and its parameters plays a crucial role in the simulation. Several research groups have studied DC operation of AlGaN/GaN HEMTs on different substrates (sapphire, <sup>16–19</sup> SiC<sup>19</sup>). Faraclas et al. <sup>20</sup> reported 2-D DC simulation and transfer characteristics along with an agreement to the experimental data. Other commercially available simulators like ATLAS (Silvaco) also be used for the demonstration of GaN based device performance.<sup>21</sup> The performance of a HEMT device suffers due to self-heating problem which occurs at higher operating voltages. The problem of self-heating arises due to the increment of lattice heat temperature that reduces mobility and hence output current reduces. This problem not only affects the performance of the device but degrade it also. To reduce the self-heating effect, employment of Silicon substrates<sup>22</sup> are one of the solutions instead of sapphire substrates. R Gaska et al.<sup>23</sup> earlier investigated self heating on GaN devices on SiC and Sapphire substrate. Chang et al.<sup>24</sup> demonstrate effects of self heating on various model parameters and Vitanov et al. 11 investigated high temperature modelling of AlGaN/GaN HEMT for DC and RF characteristics. Jie et al. 25 reported thermal effects on HEMT at the sapphire substrate. In the present work, we provide a comparison of a simulated device with the experimental results along with the effect of self-heating on the AlGaN/GaN HEMT device on Si substrate.

## II. DEVICE STRUCTURE AND SIMULATION DETAILS

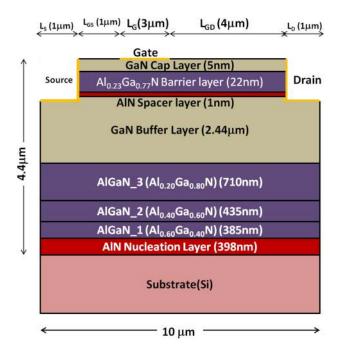

The AlGaN/GaN HEMT structures were grown on Si (111) substrates by metal organic chemical vapor deposition (MOCVD) technique. The details of the growth and epi-layer structures are discussed somewhere else. <sup>14</sup> Inductively coupled plasma etching technique was employed for the patterned mesa etching for the HEMT structure formation followed by a standard lift-off technique was employed for fabricating source/drain and gate contacts. Ohmic source and drain contacts are created by a metal stack of Ti/Al/Ni/Au followed by a rapid thermal annealing and Schottky gate contact is fabricated by Ni/Au layers. The schematic of the device structure is shown in figure 1. The current voltage characteristic of the fabricated HEMT device was measured by Agilent semiconductor analyzer.

The structure of the device has been designed in Sentaurus Device Editor (SDE) tool. The device dimensions were kept same for the experimental and simulation studies and shown in figure 1. The length of the device is 10  $\mu m$ . The Gate to Source length ( $L_{gs}$ ) is  $1\mu m$ , length of Gate ( $L_g$ ) is 3  $\mu m$  and length of Gate to Drain ( $L_{gd}$ ) is  $4\mu m$ . The simulation was carried out for DC analysis of the device at room temperature. To speed up the device simulation, silicon substrate dimensions have not been taken for the consideration and its dimensions are not affecting the DC characteristics of the device. The TCAD simulation solves three fundamental equations of the semiconductor devices namely Poisson equation, electron and hole continuity equations. These equations analyze electrical characteristics of the device. The Poisson, electron and hole continuity equations are given below in equation (1)-(3) respectively:<sup>26</sup>

$$\nabla \cdot (\varepsilon \nabla \phi) = -q (p - n + N_D - N_A) - \rho_{trap} \tag{1}$$

FIG. 1. Schematic cross-section view of Designed AlGaN/GaN HEMT.

$$\nabla \overrightarrow{J_n} = qRnet + q \frac{\partial n}{\partial t} \tag{2}$$

$$-\nabla \overrightarrow{J_p} = qRnet + q\frac{\partial p}{\partial t} \tag{3}$$

Where  $\in$  is the electrical permittivity, q electronic charge, n electron density, p hole density ,  $N_D$  ionized donor concentration,  $N_A$  ionized acceptor concentration,  $\rho_{trap}$  charge density contributed by traps,  $\varphi$  electrostatic potential,  $R_{net}$  net recombination rate,  $J_n$  electron current density and  $J_p$  the hole current density.

For calculation of bandgap, Varshni expression<sup>27</sup> is used. It shows temperature dependence of the bandgap. The expression of Varshni model is given as

$$E(T) = E_g(0) - \frac{\alpha T^2}{T + \beta} \tag{4}$$

Where  $E_g(0)$  is the bandgap of GaN at 0K temperature,  $\alpha$  is empirical constant and  $\beta$  is constant that associated with Debye temperature. The values of  $E_g(0)$ ,  $\alpha$  and  $\beta$  are 3.47eV, 7.40×10<sup>-4</sup> eV/K and 600 K extracted respectively.

The Arora<sup>28,29</sup> model is used for low field mobility analysis for both electrons and holes that is given accordingly to equation (5).

$$\mu = \mu_{min} + \frac{\mu_d}{1 + \left(\frac{N_{tot}}{N_o}\right)^{A*}} \tag{5}$$

With

$$\mu_{min} = A_{min} \left(\frac{T}{300K}\right)^{\alpha_m}, \ \mu_d = A_d \left(\frac{T}{300K}\right)^{\alpha_d}$$

$$N_0 = A_N \left(\frac{T}{300K}\right)^{\alpha_N}, A^* = A_a \left(\frac{T}{300K}\right)^{\alpha_a}$$

Where  $\mu_{min}$  is minimum mobility and  $A_{min}$ ,  $A_{max}$ ,  $\alpha_a$ ,  $A_a$ ,  $A_N$ ,  $\alpha_{N}$ ,  $\alpha_d$ ,  $\alpha_m$  are the fitting parameters. The  $A_{max}$  has been calibrated for the device low field mobility for best fit of mobility. Since Arora model is defined for InN in Sentaurus, TCAD parameters fail and require calibration. Thus the

parameter values are modified with the GaN parameters.  $^{30}$  These parameters are calibrated for our model and these are shown in Table I. The mobility  $\mu$  is used in the electron and hole continuity equations.

The mobility has been calibrated by TCAD simulation and compared with experimentally measured by hall measurement. Mobility is calculated as 1270 cm<sup>2</sup>/V.s by simulation for the device and well matched with experimentally measured mobility. The high field mobility has been modeled by Transferred Electron Effect - 2 model<sup>26</sup> in sentaurus TCAD simulator tool and is given by following equation.<sup>26,29</sup>

$$\mu = \frac{\mu_{low} + \mu_1 \left(\frac{F_{hfs}}{E_0}\right)^{\alpha} + v_{sat} \frac{F_{hfs}^{\beta - 1}}{E_1^{\beta}}}{1 + \gamma \left(\frac{F_{hfs}}{E_0}\right)^{\alpha} + \left(\frac{F_{hfs}}{E_1}\right)^{\beta}}$$

(6)

The Transferred Electron Effect -2 model comes into effect when maximum drift velocity has been reached at particular electric field. Here  $\mu_{low}$  is low field mobility and E is the electric field. The  $E_c$ ,  $F_{hfs}$ ,  $v_{sat}$ ,  $\alpha$ ,  $\beta$  and  $\gamma$  are the fitting parameters. <sup>26,29</sup>

Piezoelectric polarization effect provides information about charges at the AlGaN/GaN heterointerface and due to which forms 2DEG. Thus polarization induced sheet carrier concentration at the Al<sub>0.23</sub>Ga<sub>0.77</sub>N/ GaN is calculated by piezoelectric polarization model suggested by Ambacher *et al.*<sup>31,32</sup> The piezoelectric polarization is calculated by following equation:  $^{26,32}$

$$P_z^{pz} = 2d_{31}\sigma_1 = 2d_{31}\varepsilon_1 \left(c_{11} + c_{12} - 2\frac{c_{13}^2}{c_{33}}\right)$$

(7)

Where  $d_{31}$  is piezoelectric coefficients (cm/V),  $c_{11}$ ,  $c_{12}$ ,  $c_{13}$  and  $c_{33}$  are stiffness constants (Pa), and  $\varepsilon_1$  is strain coefficient.  $P_z^{pz}$  is piezoelectric polarization in the z direction as it is only one non vanishing component that is directed towards the growth direction. The piezoelectric charge is computed in simulation according to:<sup>26</sup>

$$q_{PE} = -activation \nabla. P_z^{pz}$$

(8)

where activation is a calibration parameter whose value is calibrated as  $\sim$ 0.38 in simulation. The  $q_{PE}$  value is added the Poisson equation:<sup>26</sup>

$$\nabla. (\in \nabla \phi) = -q(p - n + N_D - N_A + q_{PE}) \tag{9}$$

There are some allowed energy states called traps which are present in the forbidden energy level. These traps behave as recombination centers. Hence fixed interface charges, bulk and surface traps were introduced in the device analysis. In our simulation Shockely-Read-Hall recombination was used to calculate dynamic traps in the device.<sup>33</sup> It also assumes that there are traps exist at particular energy level within the bandgap. In our device simulation, sentaurus uses following set of equations.<sup>26</sup>

$$R_{net}^{SRH} = \frac{np - n_{i,eff}^2}{\tau_p (n + n_1) + \tau_n (p + p_1)}$$

(10)

with

$$n_1 = n_{i,eff} exp\left(\frac{E_{trap}}{kT}\right)$$

TABLE I. Parameters of Arora Model for GaN.

| Symbol                | Electrons              | Holes                  | Units                |

|-----------------------|------------------------|------------------------|----------------------|

| $A_{min}$             | 88                     | 54.3                   | cm <sup>2</sup> /V.s |

| $\alpha_{\mathrm{m}}$ | -6.70×10 <sup>-1</sup> | -5.70×10 <sup>-1</sup> |                      |

| $A_d$                 | 1720                   | 470                    | cm <sup>2</sup> /V.s |

| $\alpha_{ m d}$       | -4.00                  | -2.23                  |                      |

| $A_N$                 | $1.25 \times 10^{17}$  | $2.35 \times 10^{17}$  | cm <sup>-3</sup>     |

| $\alpha_{\mathbf{N}}$ | 1.9                    | 2.4                    |                      |

| $A_a$                 | $9.8 \times 10^{-1}$   | $8.8 \times 10^{-1}$   |                      |

| $\alpha_{\mathrm{a}}$ | $-1.50 \times 10^{-1}$ | -1.46×10 <sup>-1</sup> |                      |

and

$$p_1 = n_{i,eff} \exp\left(\frac{E_{trap}}{kT}\right)$$

where  $E_{trap}$  is the difference between the defect level and intrinsic level. The  $\tau_n$  and  $\tau_p$  are carrier lifetime, modelled as a product of a doping-dependent, field dependent, and temperature dependent factor:

$$\tau_c = \tau_{dop} \frac{f(T)}{1 + g_c(F)} \tag{11}$$

Where c = n and c = p for electrons and holes respectively. Since, the donor level traps are presented at the surface of the device therefore the concentration of these traps have been optimized as  $2.0 \times 10^{13} cm^{-2}$  with the energy level 0.15 eV below from the conduction band by simulation. The electron and hole capture cross-section for interface traps is about  $1 \times 10^{15}$  cm<sup>-2</sup> used for simulation.<sup>33</sup>

There is an intentional background carbon doping due to low pressure tuning  $^{14}$  at the interface of GaN/Al<sub>0.2</sub>Ga<sub>0.8</sub>N. To define carbon doping, an analytical doping profile has been created at the interface of GaN/Al<sub>0.2</sub>Ga<sub>0.8</sub>N which shows diffusion of carbon towards GaN. Therefore concentration of carbon is been optimized as  $1 \times 10^{15}$  cm<sup>-3</sup> by simulation. Thick GaN layer was grown in order to reduce buffer leakage and improve crystalline quality of the GaN epilayer. There is a very thin spacer layer (1~2 nm) of AlN above GaN layer used to reduce scattering between ionized atoms and electrons, which helps to improve the mobility of 2DEG. The AlGaN barrier layer plays an important role to improve device performance by improving sheet charges and providing low sheet resistance.

To consider the tunnelling effect in the device, Non-Local-Mesh (NLM) tunnelling<sup>26</sup> has been used in the simulation. This model is defined in TCAD simulator to describe tunneling at heterostructures, at Schottky contacts and gate leakage through thin insulator stacks. For our device, tunnelling probability of 0.22 is calculated for GaN. The tunnelling is not only due to Schottky contact or heterointerface but also due to the surface states or traps available at the top of the device. Thus, surface traps energy levels also affect the off current of the device. Generally surface traps are donor level traps which are formed due to availability of dangling bonds at the surface. The combined effect of tunnelling probability and traps gives the OFF current.

The thermodynamic model is used for analysis of self heating in the device. It is the extension of drift-diffusion approach to account for electro-thermal properties. The thermodynamic model considers an assumption that the charge carriers are in thermal equilibrium with the lattice. Hence the lattice temperature and carrier temperature are described by single temperature.<sup>34</sup> The thermodynamic model is defined by the basic set of electron and hole continuity equation and Poisson equation. These equations can be given as:<sup>26</sup>

$$\overrightarrow{J_n} = nq\mu_n(\nabla\phi_n + P_n\nabla T) \tag{12}$$

$$\overrightarrow{J_p} = nq\mu_p(\nabla\phi_p + P_p\nabla T) \tag{13}$$

Here  $P_n$  and  $P_p$  are absolute thermoelectric powers. Since HEMT devices shows self-heating thus for the accurate simulation of self heating effects, this extra driving force for the current is included.

Since HEMT devices exhibit self-heating effect thus a model for the consideration of self-heating effect is required.

In the device shown in figure 1, since there is an uninterrupted growth of GaN layer without any interlayer 14 thus we considered the heat flow from HEMT active layers to the Si substrate, in order to calculate thermal resistance. The thermal resistance can be calculated as: 24

$$R_{TH} = \frac{1}{\pi k_{Si}} ln \left( \frac{8t_{Si}}{\pi L_G} \right) \tag{14}$$

Where  $t_{Si}$  is substrate thickness,  $L_G$  is gate length, k is thermal conductivity. Where the thermal conductivity of silicon is given by:<sup>35</sup>

$$k_{Si} = 1.57 \left(\frac{T}{300}\right)^{-1.4} \tag{15}$$

The thermal resistance can relate with the effective channel temperature and power dissipated, which is given as:<sup>24</sup>

$$P_{diss} = \frac{T_{eff} - T_{sub}}{R_{TH}} \tag{16}$$

where  $T_{sub}$  is the substrate temperature. The dissipated power can be also calculated by the sum of all terminal currents multiplied by their voltages respectively. It can be given as:<sup>26</sup>

$$P_{diss} = \Sigma IV \tag{17}$$

### III. SIMULATION RESULTS AND EXPERIMENTAL VALIDATION

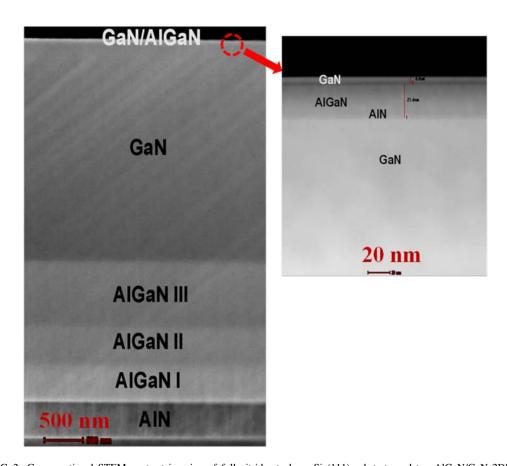

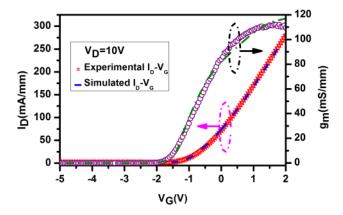

The MOCVD grown AlGaN/GaN HEMT structure on 200 mm Si (111) is used for this study. The thicknesses of all the layers were determined by STEM and shown in figure 2. To analyze the 2DEG formed at the heterointerface of Al<sub>0.23</sub>Ga<sub>0.77</sub>N/AlN/GaN, the Hall measurement has been performed. We observed a sheet resistance, mobility and carrier concentration of ~520  $\Omega/\Box$ , 1270 cm<sup>2</sup>/Vs and ~1.1x10<sup>13</sup> cm<sup>-2</sup>, respectively. This AlGaN/GaN HEMT on Si substrate is then simulated using Synopsys Sentaurus TCAD device editor (SDE) and Sentaurus device simulation (SDevice) tool using appropriate models and parameters described in section II. The validation of the device structure has been done by comparison of simulated DC transfer characteristics to experimental transfer characteristics of HEMT as shown in figure 3. The plots show good agreement between simulated and experimental transfer characteristics of the device with applied gate bias at drain voltage of 10 V. The gate bias has been varied from pinched-off region to ON state region (between -5 V to 2 V). The transconductance characteristics of simulated and experimental results also have

FIG. 2. Cross sectional STEM contrast imaging of full nitride stack on Si (111) substrate and top AlGaN/GaN 2DEG heterostructure.

FIG. 3. Experimental (star symbol) and Simulated (dashed line) Drain current vs. Gate voltage  $(I_D-V_G)$  characteristics of HEMT at  $V_D$ =10V along with Transconductance  $(g_m)$  with experimental (purple circle symbol) and simulated curve (dash dot line) at  $V_D$ =10V and 300K.

been shown in figure 3. An increment of transconductance above  $V_{GS} = -2V$  in transconductance  $(g_m)$  versus gate voltage  $(V_{GS})$  is clearly seen. This characteristics explains that at lower gate voltage  $(V_{GS} < -2V)$  channel is completely off and as the gate voltage increases above pinched off region, the channel gradually starts forming shown by figure thus we conclude that in the ON state channel resistance starts dominating.

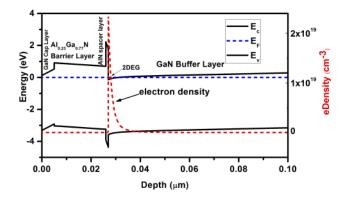

It can be seen as saturation of transconductance at higher gate voltage. The maximum transconductance has been obtained by simulation as 116.8 mS/mm at 300 K shows good agreement with the experimental data,  $115 \pm 10$  mS/mm at 300 K as shown in figure 3. The contact resistance for the device is been calculated as 0.2  $\Omega$ .mm by simulation. The charge carriers have been generated at 2DEG interface due to polarization and the sheet carrier concentration is calculated as  $3.7 \times 10^{12}$  cm<sup>-2</sup> at the interface. Due to the triangular quantum well at AlGaN/GaN heterointerface in the conduction band, the electrons confine and 2DEG forms. The band diagram of the simulated structure has shown in figure 4. At the 2DEG, the electron density is  $2 \times 10^{19}$  cm<sup>-3</sup> which provide a channel for transmission of charge carriers for device operation.

The self-heating effects are considered by calculation of lattice heat equations and these are taken in account by using thermodynamic transport model. <sup>26</sup> In this model, the drift diffusion equations are extended to accounting electro-thermal effects. Initially the charge carriers are in thermal equilibrium in lattice. Hence, in this model the charge carriers and lattice temperature are described by single temperature. Thus, a set of equations namely Poisson, electron and hole continuity equations, and lattice heat flow equation are solved in simulation. For the solution of the equations for self hating shown in section II, some thermal boundaries have been applied. Since the thermal impact of the substrate is considered as boundary conditions thus we have inserted a thermode at the interface of

FIG. 4. Band diagram of the device and electron density at 2DEG interface.

AlN and Si substrate to extract the value of TBR (thermal boundary resistance). Several simulations has been carried out and the value of TBR has been calibrated as  $1\times10^{-4}~\rm W^{-1}~cm^2$ .K, that is closed to experimentally observed value  $3.3\times10^{-4}~\rm W^{-1}~cm^2$ . K. reported by Andrei Sarua et al. <sup>36</sup> and other reports. <sup>37,38</sup> After solution of the equations, thermal resistance has been obtained 5.35 K.mm.W<sup>-1</sup> and power has been calculated as 2.8 W/mm. at  $V_{GS}$ =2V and  $V_{DS}$ =10V.

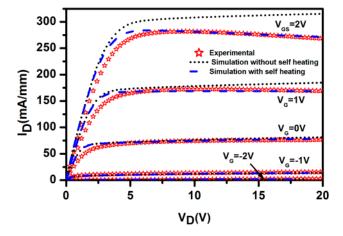

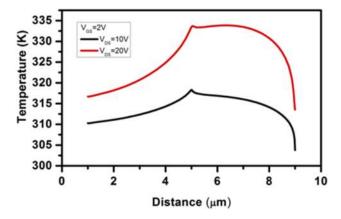

Figure 5 show the  $I_D$ - $V_D$  characteristics of the device at different  $V_{GS}$ . Here  $V_{GS}$  is varied from -2V to 2V in the step of 1V. The plots show transistors with good pinch-off characteristics. Dotted lines prescribe I-V characteristics of the device when the effects of self heating are not considered. In this case, significant deviation has been observed between experimental and simulated results. When the effect of self heating has been considered, our results were shown in figure by dashed lines in figure. The simulated I-V characteristics and experimental I-V characteristics are matched. It can be seen that at higher gate voltages the saturation current decreases as drain voltage increases this shown in figure 5. This shows effects of self heating on the device. The self heating has been observed at the gate edge between gate and drain. The maximum channel temperature at 2DEG also been observed at the gate edge between gate and drain by Kyaw *et al.*<sup>39</sup> In our simulation, the temperature analysis for self heating effect has been done by consideration of two temperature profile on the same device at different drain voltages ( $V_{DS}$ =10 V and  $V_{DS}$ =20 V) with  $V_{GS}$  = 2V. A peak of temperature of 333 K and 318 K has been observed at the gate edge between gate and drain at  $V_{DS}$  = 20 V and 10 V

FIG. 5. Variation of Drain current  $(I_D)$  and Drain voltage  $(V_D)$  for the HEMT with and without consideration of self heating effects along with experimental results. Here experimental results shown by star symbol, simulated results with self heating effect are shown by dashed lines and simulated results without self heating effect are shown by dotted lines.

FIG. 6. Effects of self heating at the 2DEG channel at VDS=10V and 20V from source to drain of the HEMT structure.

respectively as shown in figure 6. The channel temperature is low at lower  $V_{DS}$  due to low power dissipation.<sup>39</sup> Hence the simulation results with self-heating effects are validated.

### IV. CONCLUSION

The investigation on the various aspects of electrical properties of AlGaN /GaN HEMT grown on Si (111) substrate has been carried out by experimental and simulation studies. The validation of the simulation of the device has been carried out by experimental data. The results show good agreement between experimental and simulated ones. In the device simulation section, temperature dependence of the device has been considered by transport parameters and a DC characteristic of the device with the influence of self-heating effect is measured. The devices were examined in terms of piezoelectric polarization, transconductance, tunneling, surface traps and leakage. The continuity of the transconductance curve ensures about the convergence of the calculation. The agreement of experimental data and device simulation proved the simulation reliability that can be used for further analysis of the device.

- <sup>1</sup> M. Ishida, T. Ueda, T. Tanaka, and D. Ueda, IEEE Transactions on Electron Devices **60**, 3053 (2013).

- <sup>2</sup> S. Tripathy, V. K. X. Lin, S. B. Dolmanan, J. P. Y. Tan, R. S. Kajen, L. K. Bera, S. L. Teo, M. K. Kumar, S. Arulkumaran, G. I. Ng, S. Vicknesh, S. Todd, W. Z. Wang, G. Q. Lo, H. Li, D. Lee, and S. Han, Applied Physics Letters 101, 082110 (2012).

- <sup>3</sup> D. Ducatteau, A. Minko, V. Hoel, E. Morvan, E. Delos, B. Grimbert, H. Lahreche, P. Bove, C. Gaquiere, and J. De Jaeger, IEEE Electron Device Letters 27, 7 (2006).

- <sup>4</sup> J. W. Johnson, E. L. Piner, A. Vescan, R. Therrien, P. Rajagopal, J. C. Roberts, J. D. Brown, S. Singhal, and K. J. Linthicum, IEEE Electron Device Letters 25, 459 (2004).

- <sup>5</sup> P. Gangwani, S. Pandey, S. Haldar, M. Gupta, and R. Gupta, Solid-State Electronics **51**, 130 (2007).

- <sup>6</sup>G. Martin, A. Botchkarev, A. Rockett, and H. Morkoç, Applied Physics Letters **68**, 2541 (1996).

- <sup>7</sup> T. Egawa, Z. Guang-Yuan, H. Ishikawa, H. Umeno, and T. Jimbo, IEEE Transactions on Electron Devices 48, 603 (2001).

- <sup>8</sup> M. Miyoshi, T. Egawa, and H. Ishikawa, Solid-State Electronics **50**, 1515 (2006).

- <sup>9</sup> W. H. Tham, D. S. Ang, L. K. Bera, S. B. Dolmanan, T. N. Bhat, R. S. Kajen, H. R. Tan, S. L. Teo, and S. Tripathy, Journal of Vacuum Science & Technology B **34**, 041217 (2016).

- <sup>10</sup> P. Javorka, A. Alam, M. Wolter, A. Fox, M. Marso, M. Heuken, H. Luth, and P. Kordos, IEEE Electron Device Letters 23, 4 (2002).

- <sup>11</sup> M. Kumar, B. Roul, T. N. Bhat, M. K. Rajpalke, P. Mishra, L. M. Kukreha, N. Sinha, A. T. Kalghatgi, and S. B. Krupanishi, Materials Research Bulletin 45, 1581 (2010).

- <sup>12</sup> S. Boulay, S. Touati, A. A. Sar, V. Hoel, C. Gaquiere, J. C. D. Jaeger, S. Joblot, Y. Cordier, F. Semond, and J. Massies, IEEE Transactions on Electron Devices 54, 2843 (2007).

- <sup>13</sup> T. N. Bhat, M. K. Rajpalke, B. Roul, M. Kumar, and S. B. Krupanidhi, Journal of Applied Physics **110**, 093718 (2011).

- <sup>14</sup> T. N. Bhat, S. B. Dolmanan, Y. Dikme, H. R. Tan, L. K. Bera, and S. Tripathy, Journal of Vacuum Science & Technology B 32, 021206 (2014).

- <sup>15</sup> A. M. Dabiran, A. M. Wowchak, A. Osinsky, J. Xie, B. Hertog, B. Cui, D. C. Look, and P. P. Chow, Applied Physics Letters 93, 082111 (2008).

- <sup>16</sup> R. Cuerdo, F. Calle, A. Braña, Y. Cordier, M. Azize, N. Baron, S. Chenot, and E. Muñoz, Physica Status Solidi (C) 5, 1971 (2008).

- <sup>17</sup> I. Daumiller, C. Kirchner, M. Kamp, K. J. Ebeling, and E. Kohn, IEEE Electron Device Letters **20**, 448 (1999).

- <sup>18</sup> S. Sabuktagin, S. Doğan, A. A. Baski, and H. Morkoç, Applied Physics Letters **86**, 083506 (2005).

- <sup>19</sup> S. Arulkumaran, T. Egawa, H. Ishikawa, and T. Jimbo, Applied Physics Letters **80**, 2186 (2002).

- <sup>20</sup> E. W. Faraclas and A. F. M. Anwar, Solid-State Electronics **50**, 1051 (2006).

- <sup>21</sup> S. Karmalkar and U. K. Mishra, IEEE Transactions on Electron Devices **48**, 1515 (2001).

- <sup>22</sup> I. Saidi, Y. Cordier, M. Chmielowska, H. Mejri, and H. Maaref, Solid-State Electronics 61, 1 (2011).

- <sup>23</sup> R. Gaska, A. Osinsky, J. W. Yang, and M. S. Shur, IEEE Electron Device Letters 19, 89 (1998).

- <sup>24</sup> X. Cheng, M. Li, and Y. Wang, Solid-State Electronics **54**, 42 (2010).

- <sup>25</sup> S. Jie, H. Fatima, A. Koudymov, A. Chitnis, X. Hu, H. M. Wang, J. Zhang, G. Simin, J. Yang, and M. A. Khan, IEEE Electron Device Letters 24, 375 (2003).

- <sup>26</sup> Sentaurus, Version I-2013.12, Synopsys, Inc. (2013).

- <sup>27</sup> Y. P. Varshni, Physica **34**, 149 (1967).

- <sup>28</sup> N. D. Arora, J. R. Hauser, and D. J. Roulston, IEEE Transactions on Electron Devices **29**, 292 (1982).

- <sup>29</sup> G. Sabui, P. J. Parbrook, M. Arredondo-Arechavala, and Z. J. Shen, AIP Advances 6, 055006 (2016).

- <sup>30</sup> J. Piprek, Nitride Semiconductor Devices: Principles and Simulation WILEY-VCH Verlag GmbH & Co. KGaA, 76 (2007).

- <sup>31</sup> O. Ambacher, J. Majewski, C. Miskys, A. Link, M. Hermann, M. Eickhoff, M. Stutzmann, F. Bernardini, V. Fiorentini, and V. Tilak, Journal of Physics: Condensed Matter 14, 3399 (2002).

- <sup>32</sup> O. Ambacher, J. Smart, J. R. Shealy, N. G. Weimann, K. Chu, M. Murphy, W. J. Schaff, L. F. Eastman, R. Dimitrov, L. Wittmer, M. Stutzmann, W. Rieger, and J. Hilsenbeck, Journal of Applied Physics 85, 3222 (1999).

- <sup>33</sup> C. Miccoli, V. C. Martino, S. Reina, and S. Rinaudo, IEEE Electron Device Letters **34**, 1121 (2013).

- <sup>34</sup> X. D. Wang, W. D. Hu, X. S. Chen, and W. Lu, IEEE Transactions on Electron Devices **59**, 1393 (2012).

<sup>&</sup>lt;sup>35</sup> M. K. Chattopadhyaya and S. Tokekar, Microelectronics Journal 39, 1181 (2008).

<sup>36</sup> A. Sarua, H. Ji, K. P. Hilton, D. J. Wallis, M. J. Uren, T. Martin, and M. Kuball, IEEE Transactions on Electron Devices 54, 3152 (2007).

<sup>37</sup> R. Sommet, G. Mouginot, R. Quere, Z. Ouarch, and M. Camiade, Microelectronics Journal 43, 611 (2012).

38 M. Nazari, B. L. Hancock, E. L. Piner, and M. W. Holtz, IEEE Transactions on Electron Devices 62, 1467 (2015).

39 L. M. Kyaw, L. K. Bera, Y. Liu, M. K. Bera, S. P. Singh, S. B. Dolmanan, H. R. Tan, T. N. Bhat, E. F. Chor, and S. Tripathy, Applied Physics Letters 105, 073504 (2014).